■ICチップができるまで

- 成膜工程

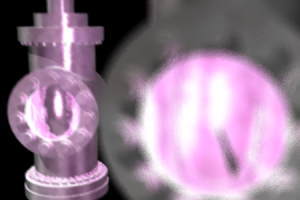

代表的な成膜方法の一つであるプラズマCVD装置(CG) |

ICチップの製造過程では、ある膜をウエハ上、もしくはそれ以前つくった膜上に成長させ、リソグラフィとエッチングで微細加工するという操作が何度も繰り返される。こうして何層もの薄膜から構成されるトランジスタなどがウエハ上に形成されていく。

薄膜の種類は多様で、例えば、MOS FETのゲート電極とチャンネル間のゲート絶縁膜(SiO2)だったり、ゲート電極に利用されるポリシリコンなどがある。いくつかの例を下の表にあげておく。(MOS

FETの構造は「トランジスタ」を参照。)

| デバイス箇所 |

薄膜の種類 |

成膜方法 |

| ゲート絶縁膜 |

SiO2 |

熱酸化法 |

| ゲート電極 |

Polycide(=WSi2+PolySi) |

PVD, CVD |

| 素子分離(フィールド) |

SiO2 |

熱酸化法、CVD |

| メタル配線 |

Al-Cu |

PVD |

| メタル配線下絶縁膜 |

SiO2, BPSG |

CVD |

| 層間絶縁膜 |

SiO2 |

熱酸化法、CVD |

| キャパシタ電極 |

PolySi |

CVD |

| キャパシタ絶縁膜 |

Si3N4+SiO2 |

CVD |

ICチップの立体構造を形成する薄膜の生成法にはいくつもの方法が挙げられるが、主なグループは、「熱酸化法」、「化学気相成長法(CVD;Chemical Vapor Deposition)」、「物理気相成長法(PVD;Physical Vapor Deposition)」の三つになる。

熱酸化法

熱酸化法はシリコンウエハを高温の酸化炉(Oxidation

Furnace)にいれ、酸素ガスやスチーム雰囲気中でシリコンと酸素を化学反応させて、二酸化シリコン膜(SiO2)を成長させる。SiO2膜は良質の絶縁層になり、半導体産業でシリコンを用いる利点の一つとなっている。

CVD、化学気相成長法 CVD、化学気相成長法

ウエハをチャンバーにいれ、薄膜の種類に応じたガスを流し込み、化学触媒反応を利用して膜を堆積する方法である。

触媒反応では、流し込まれたガスが熱やプラズマなどのエネルギーを受けとって解離し、エネルギー的に励起された前駆体ラジカルが発生する。この前駆体は下地膜表面で吸着・脱離を繰り返し、そのうちの一定量が吸着して、表面上をくまなく覆う。このとき生じる反応副生成物はガスとなって表面から脱離し、真空ポンプによって外部に排気される。

左に示したのは、減圧CVD(LP-CVD)とプラズマCVDの原理図である。

PVD、物理気相成長法

CVDが化学反応だったのに対し、PVDは物理的な過程によって成膜させる方法。具体的には、高真空中でAlなどの金属の円盤に、高エネルギーの原子(ArやそのイオンAr+)をぶつけて、玉突きの要領で金属原子を吹き飛ばしてウエハ表面に付着させるというもの。特に下の図の手法を「プレーナマグネトロンスパッタリング」と呼んでいる。

|

|